e2V

# Single-ended or Differential Clock and Analog Inputs?

# **Application Note**

#### 1. Introduction

e2v Broadband Data Conversion products are based on differential architectures chosen to optimize the devices' noise immunity.

From the input buffers down to the output buffers, all the high speed signals are handled internally in a differential fashion but does this mean that in the case of a high speed ADC, you need to drive externally the ADC in a differential fashion also?

This document is meant to resolve all your doubts about this.

This document applies to the:

- TS83102G0B 10-bit 2 Gsps ADC

- AT84AS008 10-bit 2.2 Gsps ADC

- AT84AS003 10-bit 1.5 Gsps ADC with 1:2/4 DMUX

- AT84AS004 10-bit 2 Gsps ADC with 1:2/4 DMUX

### 2. Clock Input Implementation

#### 2.1 Recommended Implementation

In the case of the TS83102G0B 10-bit 2 Gsps ADC, AT84AS008 10-bit 2.2 Gsps ADC, AT84AS003 10-bit 1.5 Gsps ADC with 1:2/4 DMUX and AT84AS004 10-bit 2 Gsps ADC with 1:2/4 DMUX, it is recommended to drive the input clock differentially.

The differential implementation is preferred to the single-ended fashion for the following reason:

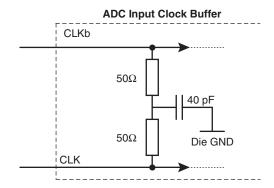

The differential input clock buffer is on-chip terminated by two  $50\Omega$  resistors connected to the die ground plane via a 40 pF capacitor (as described in Figure 2-1).

If the differential pair is used in a single-ended way (in which case, it would be necessary to terminate one signal of the pair - more likely CLKb - to ground via a  $50\Omega$  termination in order to keep the balance within the differential pair), then all the noise induced on the unused signal would affect the die ground directly and thus may degrade significantly the ADC performance.

However, this is a recommendation only. Providing a proper decoupling of the ADC power supplies to ground, the difference in performance between a differential and a single-ended use may not be significant.

Visit our website: www.e2v.com for the latest version of the datasheet

e2v semiconductors SAS 2007 0870B–BDC–06/07

Figure 2-1. Clock Input Differential Buffer

The clock inputs of the ADC have a 0V common mode and can accept signals with 1V peak maximum and -1V peak minimum.

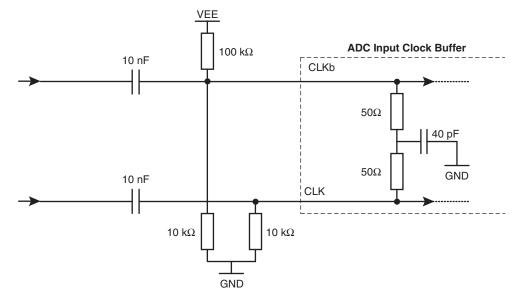

This means that if the VIH max of the signal you would like to drive the ADC clock with is higher than 1V peak or the VIL min is lower than -1V peak, then you need to AC couple the input signals before applying them to the ADC: this can be done by connecting 100 pF (or 10 nF) capacitors in series with the incoming signals to the ADC. If you do so, then you need also to bias the CLK and CLKb signals as follows:

- CLK or CLKb biased to ground via a 10  $k\Omega$  resistor

- CLKb or CLK respectively biased to ground via a 10 K $\Omega$  resistor and to V<sub>EE</sub> via a 100 k $\Omega$  resistor This will ensure that if no signal is applied to the differential pair, this one will not be floating but tied to a low level.

Figure 2-2. Recommended Clock Input AC Coupling Scheme

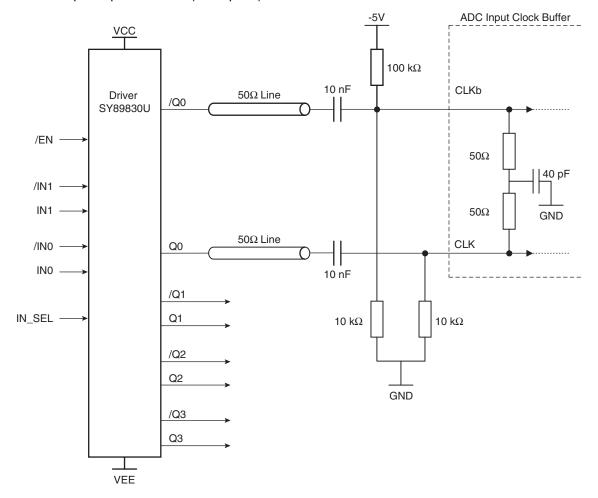

Figure 2-3. Single-Ended Scheme (Allowed But Not Recommended)

#### 2.2 Case of an Application Requiring a Fixed Clock Frequency

In the case of an application requiring a fixed clock frequency, it is recommended to filter the clock signal for improved jitter performance. The benefits of filtering the clock signal can be quantified to a 1 or 2 dB improvement in the SNR figure and thus in an increase of about 0.1 to 0.2 bit in the ENOB figure.

The filtering can be done using a narrow-band filter but because beyond the stop-band frequency the noise is not filtered out, it may be necessary to have a low pass filter after the narrow band filter.

| <b>\</b>    |                          |           |  |  |  |  |

|-------------|--------------------------|-----------|--|--|--|--|

| Filter Type | Reference                | Frequency |  |  |  |  |

| Band pass   | 4DF12-500/X2-MP (Lorch)  | 500 MHz   |  |  |  |  |

| Band pass   | 4DF12-1000/X2-MP (Lorch) | 1000 MHz  |  |  |  |  |

| Band pass   | 6DF12-1400/X2-MP (Lorch) | 1400 MHz  |  |  |  |  |

| Low pass    | 4LP7-550X-MP (Lorch)     | 550 MHz   |  |  |  |  |

| Low pass    | 5LP7-1000X-MP (Lorch)    | 1000 MHz  |  |  |  |  |

| Low pass    | 6LP7-1800X-MP (Lorch)    | 1800 MHz  |  |  |  |  |

**Table 2-1.** References for Filters (For Information Only)

## 2.3 Examples of High Speed Drivers (For Reference Only)

Table 2-2.

Differential Buffer/Gates Examples (For Information Only)

| Manufacturer          | Part Number | Description                           | Input<br>Compatibility   | Output<br>Compatibility | Max<br>Frequency | Propagation<br>Delay |

|-----------------------|-------------|---------------------------------------|--------------------------|-------------------------|------------------|----------------------|

| On Semi-<br>conductor | MC100LVEP14 | Clock Driver                          | ECL/PECL/HSTL            | ECL/PECL                | 2 GHz            | 400 ps               |

| Micrel                | SY898830    | Clock Driver                          | PECL/LVPECL/E<br>CL/HSTL | PECL                    | 2.5 GHz          | 450 ps               |

| On Semi-<br>conductor | MC10LVEP16  | Differential<br>Driver                | ECL                      | ECL                     | 4 GHz            | 240 ps               |

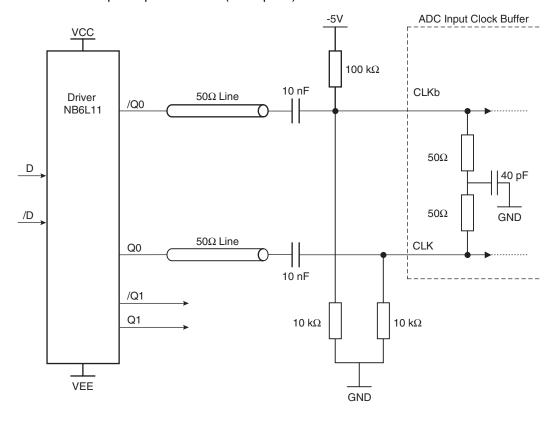

| On Semi-<br>conductor | NB6L11      | Differential<br>Driver/<br>translator | ECL                      | ECL                     | 6 GHz            | 150 ps               |

| Micrel                | SY58012U    | Differential<br>Driver/<br>translator | LVPECL/LVDS/C<br>ML      | LVPECL                  | 5 GHz            | 260 ps               |

| Micrel                | SY89311U    | Differential<br>Driver                | PECL/LVPECL/E<br>CL      | ECL/PECL                | 3 GHz            | 300 ps               |

| Micrel                | SY8985      | Differential<br>Driver/<br>translator | LVPECL/CML/LV<br>DS      | LVPECL                  | 2 GHz            | 380 ps               |

### 2.4 Practical Examples

Figure 2-4. Clock Input Implementation (Example 1)

Figure 2-5. Clock Input Implementation (Example 2)

### 3. Analog Input Implementation

#### 3.1 Recommended Implementation

Although it is necessary to drive the input clock differentially with the TS83102G0B 10-bit 2 Gsps ADC, AT84AS008 10-bit 2.2 Gsps ADC, AT84AS003 10-bit 1.5 Gsps ADC with 1:2/4 DMUX and AT84AS004 10-bit 2 Gsps ADC with 1:2/4 DMUX, the analog input can be indifferently driven single-ended or differential.

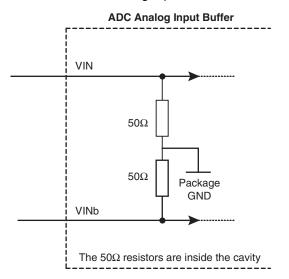

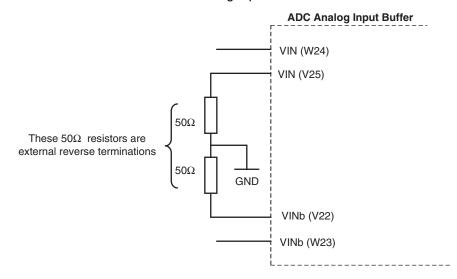

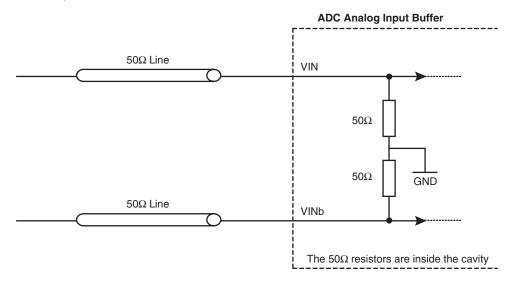

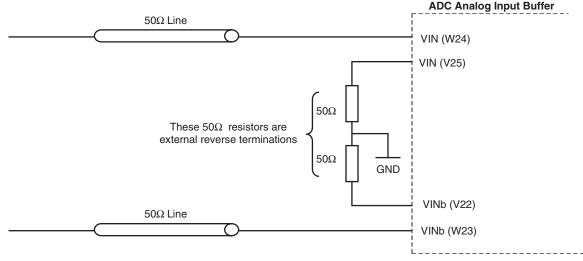

On the contrary to the differential input clock buffer, the analog input buffer is not on-chip terminated by two  $50\Omega$  resistors connected to the die ground plane but it is terminated either inside the cavity, in which case the  $50\Omega$  resistors are connected to the package ground plane (as described in Figure 3-1). or externally via  $50\Omega$  reverse termination resistors (as described in Figure 3-2).

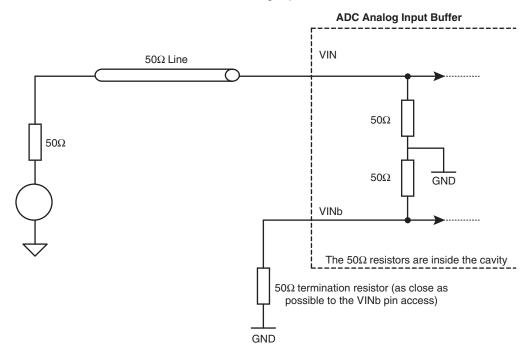

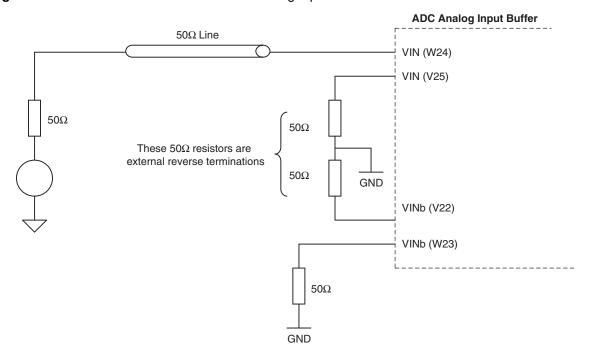

If the differential pair is used in a single-ended way (in which case, it would be necessary to terminated one signal of the pair - more likely VINb - to ground via a  $50\Omega$  termination in order to keep the balance within the differential pair), then all the noise induced on the unused signal would not affect the die ground directly.

Figure 3-1. TS83102G0B and AT84AS008 Analog Input Buffer Schematic

Figure 3-2. AT84AS003 and AT84AS004 Analog Input Buffer Schematic

### 3.2 Single-ended

#### 3.2.1 TS83102G0B, AT84AS008 Devices

Figure 3-3. TS83102G0B and AT84AS008 Analog Input Termination Scheme

#### 3.2.2 AT84AS003, AT84AS004 Devices

Figure 3-4. AT84AS003 and AT84AS004 Analog Input Termination Scheme

#### 3.3 Differential

Figure 3-5. TS83102G0B, AT84AS008 Devices

For more information concerning the conversion from a single-ended signal to a differential signal using transformers, please refer to the "Single to Differential Conversion in High Frequency applications" Application note (Ref. 5359).

Figure 3-6. AT84AS003, AT84AS004 Devices

For more information concerning the conversion from a single-ended signal to a differential signal using transformers, please refer to the "Single to Differential Conversion in High Frequency applications" Application note (Ref. 5359).

### 4. Board Layout Recommendations

There are common rules for layout of HF systems, such as the following:

- Avoid traces with angles or too many patterns (to avoid crosstalk between traces)

- Keep all traces matched to  $50\Omega$

- Have the same length for traces corresponding to signals of the same function (clock, analog in, analog out, data in, data out)

- · Avoid through hole vias for signal traces

- For differential signals, keep the True and False signal traces close to one another

- For single-ended signals, make sure that all signals are far enough from their neighbor to avoid crosstalk

In all cases, all lines should be matched to within 2 mm and the two lines of a differential pair should be matched to within 1 mm of each other.

Depending on the choice made between a single-ended or a differential mode, the board layout rules are different.

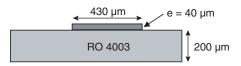

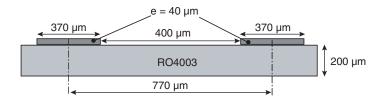

Figure 4-1 and Figure 4-2 show the recommended board layout, as used for e2v converter evaluation boards. Please note that these rules depend on the PCB material used.

**Figure 4-1.** 50 $\Omega$  Matched Line on R04003 Layout (Single-ended Signal)

Figure 4-2. 50Ω Matched Line on R04003 Layout (Differential Signal)

# e2V

#### How to reach us

Home page: www.e2v.com

Sales Office:

Northern Europe

e2v Itd

106 Waterhouse Lane

Chelmsford

Essex CM1 2QU

England

Tel: +44 (0)1245 493493 Fax:: +44 (0)1245 492492 E-Mail: enquiries@e2v.com

Southern Europe

e2v sas

16 Burospace F-91572 Bièvres

Cedex France

Tel: +33 (0) 16019 5500 Fax: +33 (0) 16019 5529 E-Mail: enquiries-fr@e2v.com

Germany and Austria

e2v gmbh

Industriestraße 29 82194 Gröbenzell

Germany

Tel: +49 (0) 8142 41057-0 Fax:: +49 (0) 8142 284547 E-Mail: enquiries-de@e2v.com **Americas**

e2v inc.

4 Westchester Plaza

Elmsford

NY 10523-1482

USA

Tel: +1 (914) 592 6050 or

1-800-342-5338,

Fax:: +1 (914) 592-5148

E-Mail: enquiries-na@e2v.com

Asia Pacific

e2v

Bank of China Tower 30th floor office 7 1 Garden Rd Central

Hong Kong

Tel: +852 2251 8227/8/9 Fax: +852 2251 8238

E-Mail: enquiries-hk@e2v.com

**Product Contact:**

e2v

Avenue de Rochepleine

BP 123 - 38521 Saint-Egrève Cedex

France

Tel: +33 (0)4 76 58 30 00

Hotline:

hotline-bdc@e2v.com

e2v semiconductors SAS 2007 0870B-BDC-06/07